Common Chipset Interconnect Specific

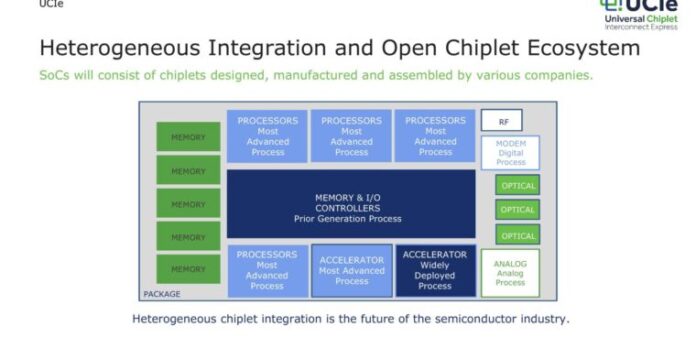

Among the CPU trade’s heaviest hitters—together with Intel, AMD, Qualcomm, Arm, TSMC, and Samsung—are banding collectively to outline a brand new normal for chiplet-based processor designs. Dubbed Common Chiplet Interconnect Specific (UCIe for brief), the brand new normal seeks to outline an open, interoperable normal for combining a number of silicon dies (or chiplets) right into a single bundle.

Intel, AMD, and others are already designing or promoting chiplet-based processors in some kind—most of AMD’s Ryzen CPUs use chiplets, and Intel’s upcoming Sapphire Rapids Xeon processors will, too. However these chips all use totally different interconnects to allow communication between chiplets. The UCIe normal, if it succeeds, will change these with a single normal, in idea making it a lot simpler for smaller corporations to benefit from chiplet-based designs or for one firm to incorporate one other firm’s silicon in its personal merchandise.

-

The UCIe (which is the identify of the specification and the group) lays out its targets in defining the UCIe normal.

Common Chipset Interconnect Specific -

The usual defines many parts of a chiplet-based design, however the interconnects and protocols used may be versatile to account for easier and extra superior designs.

Common Chipset Interconnect Specific

Chiplet-based designs are advantageous when making massive chips on cutting-edge manufacturing nodes partly as a result of they lower down on the quantity of silicon producers must throw out. If a producing defect impacts one CPU core, tossing (or binning) a single 8-core chiplet is a complete lot cheaper than having to toss an enormous 16- or 32-core processor die. Chiplet designs additionally allow you to mix-and-match chips and manufacturing processes. You can, for instance, use an older, cheaper course of on your chipset and a more recent, cutting-edge course of on your processor cores and cache. Or you could possibly put an AMD GPU on the identical bundle as an Intel CPU.

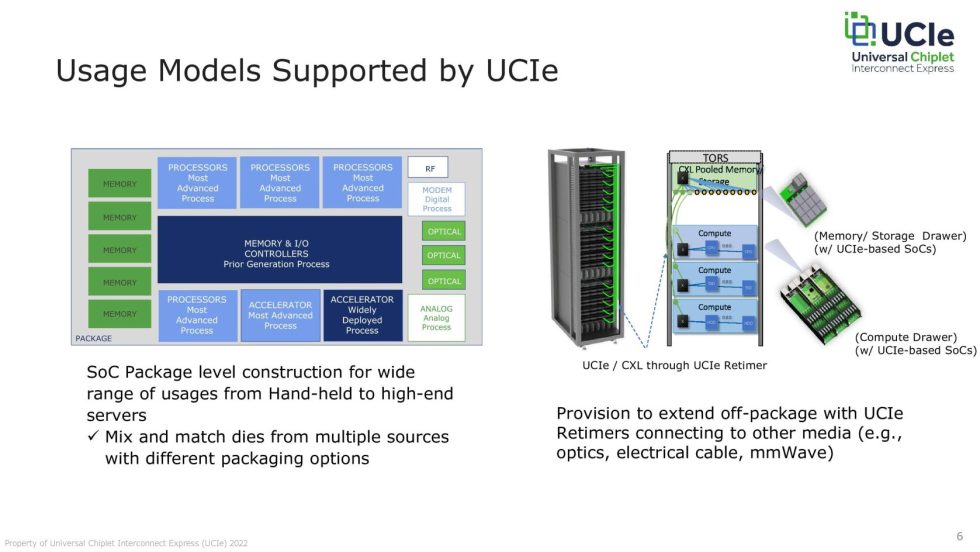

As AnandTech studies, the UCIe normal will cowl the bodily and protocol layers of chiplet design. The usual will outline how the chiplets have to be linked to one another and the protocol for facilitating communication between chiplets. However chip designers might be free to bundle these chiplets in no matter means they see match, permitting the chiplets to speak to one another instantly by way of the bundle substrate or utilizing some form of silicon-based bridge or different middleman.

Common Chipset Interconnect Specific

To accommodate these totally different bodily packaging choices, model 1.0 of UCIe defines two totally different efficiency ranges. The “normal” bundle requires 16 knowledge lanes and as a lot as 25 mm of area between chiplets, whereas the “superior” bundle makes use of 64 knowledge lanes and permits simply 2 mm of area.

The protocols underlying UCIe are PCI Specific and the associated Compute Specific Hyperlink (CXL) requirements, that are each mature and acquainted to chipmakers. However corporations which have already developed extra superior or particular protocols for inter-chiplet communication, like AMD and its Infinity Material, will be capable of use these protocols whereas remaining UCIe-compliant. UCIe was primarily developed by Intel after which donated to the broader UCIe group to function the muse for the brand new normal. However the group’s member corporations “will start work on the following era of UCIe know-how” collectively beginning later this yr.

In order for you extra technical particulars on the UCIe normal, yow will discover the white paper right here.

Itemizing picture by AMD